# 計算機システムの基礎(第9回 配布)

# 第3章 論理回路

- (1)集合

- (2)2値論理 と 基本論理回路

- (3)組み合わせ回路

- (4)順序回路

順序回路とは?、クロック フリップフロップ、レジスタ、カウンタ

担当: 福井大学 大学院工学研究科

情報・メディア工学専攻

森 眞一郎 (moris@u-fukui.ac.ip)

#### 状態を記憶する記憶回路(メモリ)を論理回路 として構成する

#### 「フリップフロップ(flip flop, FF)」

順序回路の状態を、0または1の論理値として保持するための 記憶回路(メモリ)をフリップフロップと呼ぶ。

#### フリップフロップの動作原理

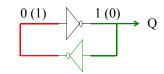

以下の2つの回路を考えてみよう。

左側の回路の出力Zは0と1を交互に繰り返し出力する(発振状態,不安定状態)。 これに対して右側の回路では、出力Qには

0または1のいずれかの値が安定して出力される(記憶状態、双安定状態)。

記憶はできるが、思い通りに記憶させるには?

#### 状態を記憶する記憶回路(メモリ)を論理回路 として構成する

#### フリップフロップの記憶状態を制御するために...

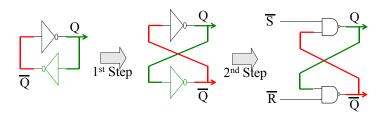

1st Step) 回路を少し書きなおします。(NOT回路の向きをそろえる)

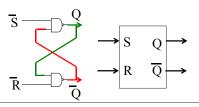

2nd Step) NOT回路をNANDに置き換えて、2つの入力端子、~Sと~Rを導入

この時、入力 🖁 と 🧵 がともに1の場合3つの回路は全て等値です。 入力がともに1でなかったら.....?

#### 状態を記憶する記憶回路(メモリ)を論理回路 として構成する

#### フリップフロップの記憶状態を制御するために...

1st Step) 回路を少し書きなおします。(NOT回路の向きをそろえる)

2nd Step) NOT回路をNANDに置き換えて、2つの入力端子、~Sと~Rを導入

| S | R | Q <sup>+</sup> | 備考   |

|---|---|----------------|------|

| 0 | 1 | 0              | リセット |

| 0 | 0 | Q              | 記憶   |

| 1 | 0 | 1              | セット  |

| 1 | 1 | 不定             | 禁止入力 |

|   |   | (不安定)          |      |

この時、入力SER がともに1の場合なぜ不定なの?

その理由は⇒ 11 ←→ 00 S.Rが共に1の間はO.Oが共に1、その後S.Rが次に共に0となると....

01

(Set Reset latch, SR latch) (教科書では RS型FFクロックなし)

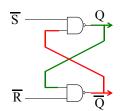

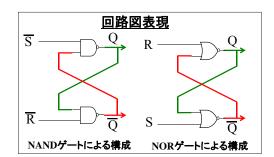

#### セット・リセット・ラッチ

(Set Reset latch, SR latch) (教科書では RS型FFクロックなし)

特性方程式は  $O^+ = S \bullet \overline{R} + \overline{S} \bullet \overline{R} \bullet O$  $0 = S \bullet R$ .....(入力条件) を整理すると  $Q^+ = S + \overline{R} \bullet Q$  $\overline{Q}^+ = R + \overline{S} \bullet \overline{Q}$

|   | 13 |                |           |

|---|----|----------------|-----------|

| S | R  | Q <sup>+</sup> |           |

| 0 | 0  | Q              | latch(保持) |

| 0 | 1  | 0              | reset     |

| 1 | 0  | 1              | set       |

| 1 | 1  | 禁止入力           |           |

# 励起表 $Q^{+}$

励起表:現在の出力QをQ+に変化 させるために必要な入力の関係を示す表

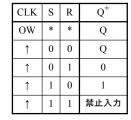

#### セット・リセット・フリップフロップ

(Set Reset flipflop, SR flipflop, SR-FF)

(同期式SRフリップフロップ Synchronous SR flipflop)

特性表

→ 同期式SR-FFの動作

- ・CLK入力が0から1に変化する瞬間 のみ SR latchと等価な動作。

- ·それ以外(otherwise:OW)は状態は不変

#### 娃性夷

| 14 11 4X |   |                |  |  |

|----------|---|----------------|--|--|

| S        | R | Q <sup>+</sup> |  |  |

| 0        | 0 | Q              |  |  |

| 0        | 1 | 0              |  |  |

| 1        | 0 | 1              |  |  |

| 1        | 1 | 禁止入力           |  |  |

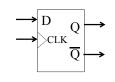

特性方程式は  $Q^+ := S + \overline{R} \bullet Q$  Dフリップフロップ(D flipflop, D-FF) (同期式Dフリップフロップ Synchronous D flipflop)

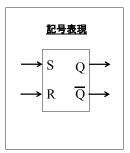

#### 記号表現

#### 特性表

| CLK | D | $Q^+$ |

|-----|---|-------|

| O.W | * | Q     |

| 1   | 0 | 0     |

| 1   | 1 | 1     |

特性方程式は  $Q^+ := D$

動作

・CLK入力が0から1に変化する瞬間に 入力Dの値を記憶する動作がおこり、 ・CLK入力がそれ以外のときは、何も変化しない

#### JKフリップフロップ(JK flipflop)

# #同期式JK-FFの 記号表現 → J Q →

# #同期式JK-FFの回路図表現 J S Q R Q R Q

#### 同期式JK-FFの特性表

| <u>同期式JK-FFの</u><br><u>記号表現</u> | CLK | J | K | Q <sup>+</sup> |        |

|---------------------------------|-----|---|---|----------------|--------|

| I                               | OW  | * | * | Q              | latch  |

| $\bigcap_{j} Q \longrightarrow$ | 1   | 0 | 0 | Q              | latch  |

| $\rightarrow$ CLK               | 1   | 0 | 1 | 0              | reset  |

| $\rightarrow$ K                 | 1   | 1 | 0 | 1              | set    |

| , pp 0 = 1 /b                   | 1   | 1 | 1 | Q              | toggle |

同期式JK-FFの動作

·CLK入力がOから1へ変化する瞬間、

J=K=1の時 トグル動作(反転)

J=K=0の時 ラッチ動作(不変/保持)

J=1,K=0の時 セット動作 J=0,K=1の時 リセット動作

・CLK入力がそれ以外(OW)のときは、状態は不変

JK-FFは、SR-FFにおける入力条件を取り除き、S=R=1に対応する J=K=1のときに出力をトグルさせるフリップフロップである。

特性方程式は

$Q^+ := (J \bullet \overline{Q} + \overline{K} \bullet Q)$

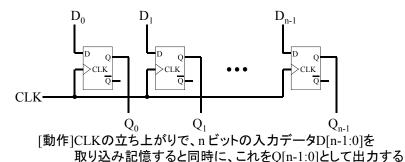

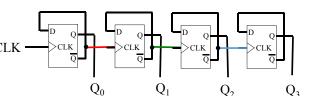

# レジスタ(Register, Reg.)

レジスタとは

数値や文字コードなど、まとまった n-bit の2値データを一時的に記憶しておくための回路

#### D-FFを使った実現例

教科書では 同期式JK-FF をつかって表現

されています

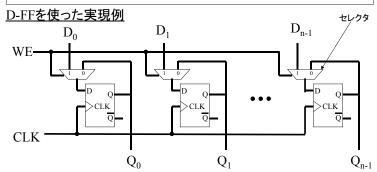

# レジスタ(Register, Reg.)

#### ホールド付レジスタ(ライトイネーブル付レジスタ)

[動作]CLKの立ち上がりで、WE=1の場合 入力データD[n-1:0]を 取り込み記憶すると同時に、これをQ[n-1:0]として出力する。 WE=0の場合、過去に記憶したデータを保持し、出力する。

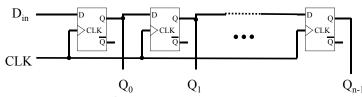

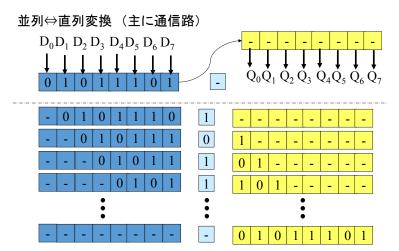

# シフトレジスタ(Shift Register)

シフトレジスタとは

レジスタに記憶された内容(データ)が、クロックに同期して 隣の桁(ビット)に順次移るレジスタ

#### 直列入力並列出力型

[動作]CLKの立ち上がりで、

0-bit目のD-FFは入力データD<sub>in</sub>を取り込み記憶すると同時に、これをQ<sub>o</sub>に出力。 i-bit目のD-FFは Q<sub>i</sub>,を取り込み記憶すると同時に、それをQ<sub>i</sub>に出力

$Q_{n-1}$ 以外の出力をなくしたもの  $\Rightarrow$  直列入力直列出力型

教科書では 同期式SR-FF をつかって表現 されています

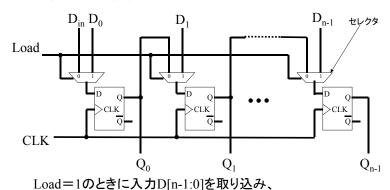

# シフトレジスタ(Shift Register)

• 並列入力並列出力型

Q<sub>n1</sub>以外の出力をなくしたもの ⇒ 並列入力直列出力型

シフトレジスタ(Shift Register)

• シフトレジスタの応用

別名 Deserializer

# シフトレジスタ(Shift Register)

Load=0のときに取り込んだ値をシフト

• シフトレジスタの応用

## 計数回路(カウンタ、Counter)

• 2進カウンタ(非同期式2進アップカウンタ)

教科書では 同期式JK-FF をつかって表現 されています

2進数表現

15

$Q_0$

$\begin{aligned} Q_1 \\ Q_2 \\ Q_3 \end{aligned}$

16

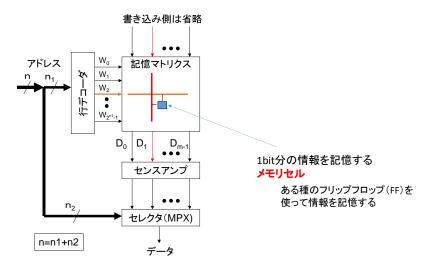

# (SRAM方式)メモリの構造(概念図)

### [レポート課題] (順序回路)

教科書P.118 演習問題 問18の応用問題

- (a)クロック同期式SR-FFを用いて、クロック同期式D-FF(の回路図)を作成せよ

- (b)クロック同期式SR-FFを用いて、クロック同期式JK-FF(の回路図)を作成せよ

- (c) クロック同期式D-FFを用いて、クロック同期式JK-FF(の回路図)を作成せよ hint1) D入力端子に ある性質をもった組み合わせ回路を接続 hint2) 両FFの特性方程式を見比べる。

(A4 レポート用紙提出のこと。表紙をつける必要はないが、1枚目の上側余白に学生番号、氏名を記入のこと 両面を使って解答してよいが、複数ページに跨る場合は必ず ホッチキス留め すること。) [A4 以外で提出した場合、ホッチキス留めがない場合は レポート点を減点します。]